# Fundamentals of Electronics

Book 1: Electronic Devices and Circuit Applications

Thomas F. Schubert, Jr. Ernest M. Kim

Synthesis Lectures on Digital Circuits and Systems

# Fundamentals of Electronics Book 1 Electronic Devices and Circuit Applications

# Synthesis Lectures on Digital Circuits and Systems

#### Editor

#### Mitchell A. Thornton, Southern Methodist University

The *Synthesis Lectures on Digital Circuits and Systems* series is comprised of 50- to 100-page books targeted for audience members with a wide-ranging background. The Lectures include topics that are of interest to students, professionals, and researchers in the area of design and analysis of digital circuits and systems. Each Lecture is self-contained and focuses on the background information required to understand the subject matter and practical case studies that illustrate applications. The format of a Lecture is structured such that each will be devoted to a specific topic in digital circuits and systems rather than a larger overview of several topics such as that found in a comprehensive handbook. The Lectures cover both well-established areas as well as newly developed or emerging material in digital circuits and systems design and analysis.

Fundamentals of Electronics: Book 1 Electronic Devices and Circuit Applications Thomas F. Schubert, Jr. and Ernest M. Kim 2015

Applications of Zero-Suppressed Decision Diagrams Tsutomu Sasao and Jon T. Butler 2014

Modeling Digital Switching Circuits with Linear Algebra Mitchell A. Thornton 2014

Arduino Microcontroller Processing for Everyone! Third Edition Steven F. Barrett 2013

Boolean Differential Equations Bernd Steinbach and Christian Posthoff 2013

Bad to the Bone: Crafting Electronic Systems with BeagleBone and BeagleBone Black Steven F. Barrett and Jason Kridner 2013

#### Introduction to Noise-Resilient Computing

S.N. Yanushkevich, S. Kasai, G. Tangim, A.H. Tran, T. Mohamed, and V.P. Shmerko 2013

Atmel AVR Microcontroller Primer: Programming and Interfacing, Second Edition Steven F. Barrett and Daniel J. Pack 2012

#### Representation of Multiple-Valued Logic Functions

Radomir S. Stankovic, Jaakko T. Astola, and Claudio Moraga 2012

Arduino Microcontroller: Processing for Everyone! Second Edition

Steven F. Barrett

2012

#### Advanced Circuit Simulation Using Multisim Workbench

David Báez-López, Félix E. Guerrero-Castro, and Ofelia Delfina Cervantes-Villagómez 2012

#### Circuit Analysis with Multisim

David Báez-López and Félix E. Guerrero-Castro 2011

Microcontroller Programming and Interfacing Texas Instruments MSP430, Part I Steven F. Barrett and Daniel J. Pack 2011

Microcontroller Programming and Interfacing Texas Instruments MSP430, Part II Steven F. Barrett and Daniel J. Pack 2011

#### Pragmatic Electrical Engineering: Systems and Instruments

William Eccles

2011

#### Pragmatic Electrical Engineering: Fundamentals

William Eccles

2011

Introduction to Embedded Systems: Using ANSI C and the Arduino Development Environment

David J. Russell

2010

Arduino Microcontroller: Processing for Everyone! Part II

Steven F. Barrett

2010

#### Arduino Microcontroller Processing for Everyone! Part I

Steven F. Barrett 2010

#### Digital System Verification: A Combined Formal Methods and Simulation Framework Lun Li and Mitchell A. Thornton 2010

#### Progress in Applications of Boolean Functions

Tsutomu Sasao and Jon T. Butler 2009

#### Embedded Systems Design with the Atmel AVR Microcontroller: Part II

Steven F. Barrett

2009

#### Embedded Systems Design with the Atmel AVR Microcontroller: Part I

Steven F. Barrett

2009

### Embedded Systems Interfacing for Engineers using the Freescale HCS08 Microcontroller II: Digital and Analog Hardware Interfacing

Douglas H. Summerville

2009

#### Designing Asynchronous Circuits using NULL Convention Logic (NCL)

Scott C. Smith and JiaDi

2009

### Embedded Systems Interfacing for Engineers using the Freescale HCS08 Microcontroller I: Assembly Language Programming

Douglas H.Summerville

2009

#### Developing Embedded Software using DaVinci & OMAP Technology

B.I. (Raj) Pawate

2009

#### Mismatch and Noise in Modern IC Processes

Andrew Marshall

2009

### Asynchronous Sequential Machine Design and Analysis: A Comprehensive Development of the Design and Analysis of Clock-Independent State Machines and Systems

Richard F. Tinder

2009

#### An Introduction to Logic Circuit Testing

Parag K. Lala

2008

#### Pragmatic Power

William J. Eccles 2008

#### Multiple Valued Logic: Concepts and Representations

D. Michael Miller and Mitchell A. Thornton 2007

#### Finite State Machine Datapath Design, Optimization, and Implementation

Justin Davis and Robert Reese 2007

#### Atmel AVR Microcontroller Primer: Programming and Interfacing

Steven F. Barrett and Daniel J. Pack 2007

#### Pragmatic Logic

William J. Eccles 2007

#### PSpice for Filters and Transmission Lines

Paul Tobin 2007

#### PSpice for Digital Signal Processing

Paul Tobin 2007

#### PSpice for Analog Communications Engineering

Paul Tobin 2007

#### PSpice for Digital Communications Engineering

Paul Tobin 2007

#### PSpice for Circuit Theory and Electronic Devices

Paul Tobin 2007

#### Pragmatic Circuits: DC and Time Domain

William J. Eccles

2006

#### Pragmatic Circuits: Frequency Domain

William J. Eccles

2006

## Pragmatic Circuits: Signals and Filters William J. Eccles

2006

# High-Speed Digital System Design Justin Davis

2006

#### Introduction to Logic Synthesis using Verilog HDL

Robert B.Reese and Mitchell A.Thornton 2006

#### Microcontrollers Fundamentals for Engineers and Scientists

Steven F. Barrett and Daniel J. Pack 2006

#### Copyright © 2014 by Morgan & Claypool

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means—electronic, mechanical, photocopy, recording, or any other except for brief quotations in printed reviews, without the prior permission of the publisher.

Fundamentals of Electronics: Book 1 Electronic Devices and Circuit Applications

Thomas F. Schubert, Jr. and Ernest M. Kim

www.morganclaypool.com

ISBN: 9781627055628 paperback ISBN: 9781627055635 ebook

DOI 10.2200/S00598ED1V01Y201409DCS045

A Publication in the Morgan & Claypool Publishers series SYNTHESIS LECTURES ON DIGITAL CIRCUITS AND SYSTEMS

Lecture #45

Series Editor: Mitchell A. Thornton, Southern Methodist University

Series ISSN

Print 1932-3166 Electronic 1932-3174

# Fundamentals of Electronics Book 1

# **Electronic Devices and Circuit Applications**

Thomas F. Schubert, Jr. and Ernest M. Kim University of San Diego

SYNTHESIS LECTURES ON DIGITAL CIRCUITS AND SYSTEMS #45

#### **ABSTRACT**

This book, *Electronic Devices and Circuit Application*, is the first of four books of a larger work, *Fundamentals of Electronics*. It is comprised of four chapters describing the basic operation of each of the four fundamental building blocks of modern electronics: operational amplifiers, semiconductor diodes, bipolar junction transistors, and field effect transistors. Attention is focused on the reader obtaining a clear understanding of each of the devices when it is operated in equilibrium. Ideas fundamental to the study of electronic circuits are also developed in the book at a basic level to lessen the possibility of misunderstandings at a higher level. The difference between linear and non-linear operation is explored through the use of a variety of circuit examples including amplifiers constructed with operational amplifiers as the fundamental component and elementary digital logic gates constructed with various transistor types.

Fundamentals of Electronics has been designed primarily for use in an upper division course in electronics for electrical engineering students. Typically such a course spans a full academic years consisting of two semesters or three quarters. As such, Electronic Devices and Circuit Applications, and the following two books, Amplifiers: Analysis and Design and Active Filters and Amplifier Frequency Response, form an appropriate body of material for such a course. Secondary applications include the use in a one-semester electronics course for engineers or as a reference for practicing engineers.

#### **KEYWORDS**

operational amplifiers, amplifiers, modeling, gain, semiconductor diodes, load lines, zener diodes, rectifiers, logic gates, transistors, bipolar junction transistors, TTL, ECL, transistor biasing, bias stability, field effect transistors, BJT, FET, MOSFET, SPICE modeling

# **Contents**

|   | Pref | ace xv                                                                         |

|---|------|--------------------------------------------------------------------------------|

|   | Ack  | nowledgmentsxvii                                                               |

| 1 | Ope  | rational Amplifiers and Applications                                           |

|   | 1.1  | Basic Amplifier Characteristics                                                |

|   | 1.2  | Modeling the OpAmp                                                             |

|   | 1.3  | Basic Applications of the OpAmp                                                |

|   |      | 1.3.1 Inverting Amplifier                                                      |

|   |      | 1.3.2 Summing Amplifier                                                        |

|   |      | 1.3.3 Non-inverting Amplifier                                                  |

|   |      | 1.3.4 Difference Amplifier                                                     |

|   |      | 1.3.5 Integrator                                                               |

|   |      | 1.3.6 Differentiator                                                           |

|   | 1.4  | Differential Amplifiers                                                        |

|   | 1.5  | Non-Ideal Characteristics of OpAmps                                            |

|   |      | 1.5.1 Finite Gain, Finite Input Resistance and Non-zero Output Resistance . 34 |

|   |      | 1.5.2 Input Parameter Variations                                               |

|   |      | 1.5.3 Output Parameter Limitations                                             |

|   |      | 1.5.4 Package and Supply Related Parameters                                    |

|   | 1.6  | Concluding Remarks                                                             |

|   | 1.7  | Problems                                                                       |

|   | 1.8  | References                                                                     |

| 2 | Dio  | de Characteristics and Circuits                                                |

|   | 2.1  | Basic Functional Requirements of an Ideal Diode                                |

|   | 2.2  | Semiconductor Diode Volt-Ampere Relationship                                   |

|   | 2.3  | The Diode as a Circuit Element                                                 |

|   |      | 2.3.1 Numerical Solutions                                                      |

|   |      | 2.3.2 Simulation Solutions                                                     |

|   | 2.4  | Load Lines                                                                     |

|   |      | 2.4.1 Graphical Solutions to Static Circuits                    | 73             |

|---|------|-----------------------------------------------------------------|----------------|

|   |      | 2.4.2 Graphical Solutions to Circuits with Time Varying Sources | 74             |

|   | 2.5  | Simplified Piecewise Linear Models of the Diode                 | 75             |

|   |      | 2.5.1 Forward Bias Modeling                                     | <sup>7</sup> 6 |

|   |      | 2.5.2 Reverse Bias Modeling                                     | 32             |

|   | 2.6  | Diode Applications                                              | 33             |

|   |      | 2.6.1 Limiter or Clipping Circuit                               | 34             |

|   |      | 2.6.2 Half-Wave Rectifiers                                      | 38             |

|   |      | 2.6.3 Full-Wave Rectifiers                                      |                |

|   |      | 2.6.4 Peak Detector                                             |                |

|   |      | 2.6.5 Clamping or DC Restoring Circuits                         |                |

|   |      | 2.6.6 Voltage Multiplier                                        |                |

|   |      | 2.6.7 Diode Logic Gates                                         |                |

|   |      | 2.6.8 The Superdiode                                            |                |

|   | 2.7  | Zener Diodes and Applications                                   |                |

|   | 2.8  | Other Common Diodes and Applications                            |                |

|   |      | 2.8.1 Tunnel Diode                                              |                |

|   |      | 2.8.2 Schottky Barrier Diode                                    |                |

|   |      | 2.8.3 Photodiode                                                |                |

|   | 2.0  | 2.8.4 Light-Emitting Diode                                      |                |

|   | 2.9  | Concluding Remarks                                              |                |

|   | 2.10 | Problems                                                        |                |

|   | 2.11 | References                                                      | 30             |

| 3 | Bipo | lar Junction Transistor Characteristic                          | 3              |

|   | 3.1  | BJT <i>V-I</i> Relationships                                    | 34             |

|   | 3.2  | The BJT as a Circuit Element                                    | 39             |

|   | 3.3  | Regions of Operation in BJTs                                    | 15             |

|   | 3.4  | Modeling the BJT in its Regions of Operation                    | 17             |

|   | 3.5  | Digital Electronics Applications                                |                |

|   |      | 3.5.1 A Logic Inverter Circuit                                  |                |

|   |      | 3.5.2 Diode-Transistor Logic Gate                               |                |

|   |      | 3.5.3 Transistor-Transistor Logic Gate                          |                |

|   |      | 3.5.4 Emitter-Coupled Logic Gate                                |                |

|   | 3.6  | Biasing the Bipolar Junction Transistor                         | 57             |

|   |      | 3.6.1 Fixed-Bias Circuit                                        |                |

|   |   | ٠ | ٠ |

|---|---|---|---|

| v | п | 1 | 1 |

|   |       | All                                                          |

|---|-------|--------------------------------------------------------------|

|   |       | 3.6.2 Emitter-Bias Circuit (With Two Power Supplies)         |

|   |       | 3.6.3 Self-Bias Circuit (Emitter-Bias with One Power Supply) |

|   |       | 3.6.4 Biasing <i>pnp</i> Transistors                         |

|   | 3.7   | Bias Stability                                               |

|   |       | 3.7.1 Fixed-Bias Circuit Stability                           |

|   |       | 3.7.2 Self-Bias Circuit Stability                            |

|   | 3.8   | Concluding Remarks                                           |

|   | 3.9   | Problems                                                     |

|   | 3.10  | References                                                   |

| 4 | Field | Effect Transistor Characteristics                            |

|   | 4.1   | Juction Field-Effect Transistors                             |

|   |       | 4.1.1 <i>n</i> -channel JFET                                 |

|   |       | 4.1.2 The <i>p</i> -channel JFET                             |

|   | 4.2   | Metal-Oxide-Semiconductor Field-Effect Transistors           |

|   |       | 4.2.1 Depletion-Type MOSFET                                  |

|   |       | 4.2.2 Depletion-type PMOSFET                                 |

|   |       | 4.2.3 Enhancement Type MOSFETs                               |

|   |       | 4.2.4 Enhancement Type NMOSFET                               |

|   |       | 4.2.5 Enhancement Type PMOSFET                               |

|   | 4.3   | The FET as a Circuit Element                                 |

|   |       | 4.3.1 FET SPICE models                                       |

|   |       | 4.3.2 FET as a Voltage Variable Resistor                     |

|   |       | 4.3.3 <i>n</i> -JFET as a Constant-Current Source            |

|   |       | 4.3.4 FET Inverter                                           |

|   |       | 4.3.5 FET as an Active Load                                  |

|   |       | 4.3.6 CMOS Inverter                                          |

|   | 4.4   | Regions of Operations in FETs                                |

|   | 4.5   | The FET as an Analog Switch                                  |

|   | 4.6   | Biasing the FET                                              |

|   |       | 4.6.1 The Source Self-Bias Circuit                           |

|   |       | 4.6.2 The Fixed-Bias Circuit                                 |

|   |       | 4.6.3 Biasing Enhancement mode FETs                          |

|   | 4.7   | Concluding Remarks                                           |

|   | 4.8   | Problems                                                     |

|   | 4.9   | References                                                   |

| xiv                  |     |

|----------------------|-----|

| Authors' Biographies | 299 |

|                      |     |

|                      |     |

|                      |     |

|                      |     |

|                      |     |

|                      |     |

|                      |     |

|                      |     |

|                      |     |

|                      |     |

|                      |     |

|                      |     |

|                      |     |

|                      |     |

|                      |     |

|                      |     |

|                      |     |

|                      |     |

|                      |     |

### **Preface**

It is expected that the reader of this text is familiar with the common passive elements of linear circuit analysis (resistors, inductors, capacitors, and transformers) as well as the idealized linear active elements (independent and dependent voltage and current sources). Unfortunately, the field of electronics makes great use of active elements that do not necessarily fall into either of the above categories. These active elements may behave in either a linear or non-linear fashion depending on their circuit application.

The study of electronic circuit behavior traditionally begins with three active semiconductor electronic elements:

- The Semiconductor Diode

- The Bipolar Junction Transistor (BJT)

- The Field Effect Transistor (FET)

To this trio of fundamental devices has been added an additional electronic circuit building block, the Operational Amplifier (OpAmp). While the OpAmp is composed of tens of transistors (usually either BJTs or FETs, but sometimes a mixture of both types) and often a few diodes, its easily understood terminal properties, high use in industry, and commercial availability make it a good companion for study with the other devices.

Quasistatic analysis explores the potentially non-linear action of each of these four elements (or any other similar element) in a variety of applications. The fundamental assumption in this exploration is that voltage and current transitions take place slowly and that the circuit is always in equilibrium: hence the term quasistatic.

The authors have chosen to begin the study of electronics with a chapter on the operational amplifier for several reasons, among which are:

- in most simple applications, the OpAmp behaves in a near-ideal fashion.

- typical analysis of OpAmp circuitry provides a good review of basic circuit analysis techniques.

- discussion of the OpAmp provides a good framework for understanding of electronic circuitry.

While many readers will find much in this chapter on OpAmps a review, the chapter presents several concepts fundamental to the study of electronic circuitry. Most significant among these concepts are:

#### xvi PREFACE

- · undistorted amplification

- gain

- · device modeling

- conditions under which device models, particularly linear models, fail

Of particular importance is the concept that a device with extremely complex interior working mechanisms can be modeled simply by its terminal characteristics.

The remaining three chapters in this book present the semiconductor diode, the BJT and the FET. Each chapter follows the same basic framework and has the same goals:

- To present each device through real experimental data and through theoretical functional relationships.

- To use the above presented relationships to observe the action of the device in relatively simple circuits.

- To devise a progression of realistic piecewise-linear models for the devices. The theoretical basis for each model is presented and the appropriate use of these models is explored. Only when a model fails to properly predict device behavior will new, more complex, models be introduced. This simple-to-complex route provides for progressively more detailed analysis using the newly introduced models.

- To use realistic applications to demonstrate the usefulness of the device models.

- To provide a solid foundation for the linear and non-linear modeling and applications found in later books of this series.

Upon completing Book 1, the reader will have a good foundation in the operation of these four basic active, non-linear devices. The fundamental regions of operation for each device will have been explored: both linear and non-linear device models will be available for further investigations.

Thomas F. Schubert, Jr. and Ernest M. Kim May 2015

# Acknowledgments

In the development of any book, it seems that an infinite number of people provide and incalculable amount of guidance and help. While our thanks goes out to all those who helped, us, we can only mention a few of our many benefactors here. Special thanks go to Lynn Cox, who sparked our interest in writing an electronics text and, of course, to the staff at Morgan and Claypool Publishers, specifically Joe Claypool and Dr. C.L. Tondo.

Thomas F. Schubert, Jr. and Ernest M. Kim May 2015

# Operational Amplifiers and Applications

The Operational Amplifier (commonly referred to as the OpAmp) is one of the primary active devices used to design low and intermediate frequency analog electronic circuitry: its importance is surpassed only by the transistor. OpAmps have gained wide acceptance as electronic building blocks that are useful, predictable, and economical. Understanding OpAmp operation is fundamental to the study of electronics.

The name, operational amplifier, is derived from the ease with which this fundamental building block can be configured, with the addition of minimal external circuitry, to perform a wide variety of linear and non-linear circuit functions. Originally implemented with vacuum tubes and now as small, transistorized integrated circuits, OpAmps can be found in applications such as: signal processors (filters, limiters, synthesizers, etc.), communication circuits (oscillators, modulators, demodulators, phase-locked loops, etc.), Analog/Digital converters (both A to D and D to A), and circuitry performing a variety of mathematical operations (multipliers, dividers, adders, etc.).

The study of OpAmps as circuit building blocks is an excellent starting point in the study of electronics. The art of electronics circuit and system design and analysis is founded on circuit realizations created by interfacing building block elements that have specific terminal characteristics. OpAmps, with near-ideal behavior and electrically good interconnection properties, are relatively simple to describe as circuit building blocks.

Circuit building blocks, such as the OpAmp, are primarily described by their terminal characteristics. Often this level of modeling complexity is sufficient and appropriately uncomplicated for electronic circuit design and analysis. However, it is often necessary to increase the complexity of the model to simplify the analysis and design procedures. These models are constructed from basic circuit elements so that they match the terminal characteristics of the device. Resistors, capacitors, and voltage and current sources are the most common elements used to create such a model: an OpAmp can be described at a basic level with two resistors and a voltage-controlled voltage source.

OpAmp circuit analysis also offers a good review of fundamental circuit analysis techniques. From this solid foundation, the building block concept is explored and expanded throughout this text. With the building block concept, all active devices are treated as functional blocks with specified input and output characteristics derived from the device terminal behavior. Circuit design is

the process of interconnecting active building blocks with passive components to produce a wide variety of desired electronic functions.

#### 1.1 BASIC AMPLIFIER CHARACTERISTICS

One of the fundamental characteristics of an amplifier is its gain. Gain is defined as the factor that relates the output to the input signal intensities. As shown in Figure 1.1, a time dependent input signal, x(t), is introduced to the "black box" which represents an amplifier and another time dependent signal, y(t), appears at the output.

$$x(t) \circ A \longrightarrow y(t)$$

**Figure 1.1:** "Black box" representation of an amplifier with input  $\mathbf{x}(t)$  and output  $\mathbf{y}(t)$ .

In actuality,  $\mathbf{x}(t)$  can represent either a time dependent or time independent signal. The output of a good amplifier,  $\mathbf{y}(t)$ , is of the same functional form as the input with two significant differences: the magnitude of the output is scaled by a constant factor, A, and the output is delayed by a time,  $t_d$ . This input-output relationship can be expressed as:

$$\mathbf{y}(t) = A\mathbf{x}(t - t_d) + \alpha \tag{1.1}$$

where

A is the gain of the amplifier,

$\alpha$  is the output DC offset, and

$t_d$  is the time delay between the input and output signals.

The signal is "amplified" by a factor of A. Amplification is a ratio of output signal level to the input signal level. The output signal is amplified when |A| is greater than 1. For |A| less than 1, the output signal is said to be attenuated. If A is a negative value, the amplifier is said to invert the input. Should x(t) be sinusoidal, inversion of a signal is equivalent to a phase shift of  $180^\circ$ : negative A implies the output signal is  $\pm 180^\circ$  out of phase with the input signal.

For time-varying signals, it may be convenient to find the amplification (ratio) by comparing either the root-mean-squared (RMS) values or the peak values of the input and output signals. Good measurement technique dictates that amplification is found by measuring the input and output RMS values since peak values may, in many instances, be ambiguous and difficult to quantify. Unfortunately, in many practical instances, RMS or power meters are not available dictating the measurement of peak amplitudes. The delay time is an important quantity that is

<sup>&</sup>lt;sup>1</sup>Other amplifier specifications of interest include input and output impedances, power consumption, frequency response, noise factor, Mean Time to Failure (MTTF), and operational temperature range. An understanding of the basis for these specifications and their impact on design will be developed in the chapters that follow. The discussion in this chapter will, for the most part, be restricted to gain and time-domain effects.

<sup>&</sup>lt;sup>2</sup>Peak values are also strongly affected by the presence of noise.

often overlooked in electronic circuit analysis and design.<sup>3</sup> The signal encounters delay between the input and output of an amplifier simply because it must propagate through a number of the internal components of the amplifying block.

In Figure 1.1,  $\mathbf{x}(t)$  and  $\mathbf{y}(t)$  are time dependent signals. Depending on the amplifier,  $\mathbf{x}(t)$  and  $\mathbf{y}(t)$  can be either current or voltage signals. Every amplifier draws power from a power supply, typically in the form of current from a DC voltage source. As will be shown in later sections of this text, the maximum possible output signal level is determined largely by the power supply voltage and current limitations. For instance, assume that the amplifier in Figure 1.1 is powered by a DC voltage source with output equal to  $V_{CC}$ . If the output signal,  $\mathbf{y}(t)$ , is a voltage signal, the maximum output voltage attainable under ideal conditions for the gain block is  $V_{CC}$ . The phenomenon of limiting output voltage levels to lie within the limits set by the power supplies is called *saturation*. Should the power supply be unable to provide sufficient current to the gain block, the output will also be limited, although in a manner that is not as simple as in saturation.

In order to discuss terminal characteristics of commercially available OpAmps, a specific amplifier must be selected. The  $\mu$ A741 (or LM741, MC1741) is a good choice since it is the most commonly used and studied OpAmp available. The prefixes { $\mu$ A, OP, LM, MC} designate the manufacturer of the integrated circuit (IC):  $\mu$ A represents Fairchild Semiconductor, OP is used by Linear Technologies, LM by National Semiconductor, and MC by Motorola Semiconductors. The specification sheets for the three OpAmps listed above can be found on the internet. In many instances, one or two letters follow the numerical designation of the IC. These letters indicate the package type or size and package material. For example, a  $\mu$ A741CP is a 741 IC manufactured by National Semiconductor that is in a commercial grade plastic standard eight lead dual-in-line package (DIP) or MINI DIP. Other manufacturers, such as Texas Instruments, manufacture the  $\mu$ A741CP using the Fairchild part designation.

Other common OpAmps include the OP-27, LF411, and LM324. The OP-27 and LF411 OpAmps have specifications that are similar to the  $\mu$ A741 and come in selected packages. The OP-27 and LF411 OpAmps are, like the  $\mu$ A741, dual power rail amplifiers; that is, the amplifier usually operates with both a positive and negative power supply voltages. The LM324, on the other hand, is a single supply amplifier; it requires a positive voltage and a common reference (ground).

Figure 1.2 shows a top view of a  $\mu$ A741CP package with the terminal designations. The terminals of interest are:

- the inverting input (pin 2),

- the non-inverting input (pin 3),

<sup>&</sup>lt;sup>3</sup>The implication of delay time is addressed in the transistor amplifier time domain analysis portion of the third book of this series.

<sup>&</sup>lt;sup>4</sup>Note that upper case letters are used for DC signals and lower case letters for time-varying signals. Lower case letters with lower case subscripts is used for AC signals. Lower case letters with upper case subscripts are used for AC signals with DC components.

- the output (pin 6),

- the positive power supply (designated  $+V_{cc}$ , pin 7), and

- the negative power supply (designated  $-V_{cc}$ , pin 4).

The offset null pins (1 and 5) are used to compensate for minor fabrication imperfections as well as degradation due to aging. Although commonly left disconnected by the circuit designer, these pins are sometimes utilized in applications that require the amplification of very small level signals. The  $\mu$ A741 OpAmp is a compensated amplifier. The performance implications of compensated and uncompensated amplifiers are related to frequency response and stability: they will be discussed in detail in the third book of this series.

**Figure 1.2:** The top view of the  $\mu$ A741CP package with pin numbers.

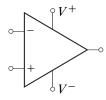

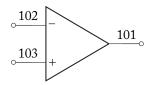

A conventional simplified OpAmp schematic representation is shown in Figure 1.3. This representation shows two input terminals designated (-) and (+) corresponding to the inverting and non-inverting inputs, respectively, the output terminal, and the positive and negative power supply terminals labeled  $V^+$  and  $V^-$ , respectively. Not shown are the offset null pins. Unless used, these pins are usually not included in schematic representations.

**Figure 1.3:** OpAmp schematic representation.

Notice that the schematic symbol of the OpAmp does not have a ground pin. In many ways, the lack of a ground pin on the OpAmp is the key to its operation. Ideally, only the differential voltage between the two input pins affects the output voltage of an OpAmp. A ground reference is provided external to the chip package.

#### 1.2 MODELING THE OPAMP

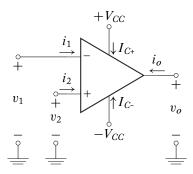

Terminal voltages and currents are used to characterize OpAmp behavior. In order to unify all discussions of OpAmp circuitry, it is necessary to define appropriate descriptive conventions. All voltages are measured relative to a common reference node (or ground) which is external to the chip as is shown in Figure 1.4. The voltage between the inverting pin and ground is denoted as  $v_1$ : the voltage between the non-inverting pin and ground is  $v_2$ . The output voltage referenced to ground is denoted as  $v_o$ . Power is typically applied to an OpAmp in the form of two equalmagnitude supplies, denoted  $V_{CC}$  and  $-V_{CC}$ , which are connected to the V<sup>+</sup> and V<sup>-</sup> terminals of the OpAmp, respectively.

The reference current directions are shown in Figure 1.4. The direction of current flow is always into the nodes of the Op Amp. The current into the inverting input terminal is  $i_1$ ; current into the non-inverting input terminal is  $i_2$ ; current into the output terminal is  $i_0$ ; and the currents into the positive and negative power supply terminals are  $I_{C-}$  and  $I_{C+}$ , respectively.

Figure 1.4: Terminal voltages and currents.

The voltage and current constraints inherent to the input and output terminals of an OpAmp must be understood prior to connecting external circuit elements. The OpAmp is considered as a building block element with specific rules of operation. A short discussion of these rules of operation follows.

The terminal voltages are constrained by the following relationships<sup>5</sup>

$$v_o = A(v_2 - v_1) (1.2)$$

and

$$-V_{CC} \le v_o \le V_{CC}. \tag{1.3}$$

The first of the two voltage constraints states that the output voltage is proportional to the difference between the non-inverting and inverting terminal inputs,  $v_2$  and  $v_1$ , respectively. The

$<sup>^5</sup>$ For introductory purposes, the time delay factor  $t_d$  has been assumed to be zero. Delay time considerations will be discussed at length in the third book of this series.

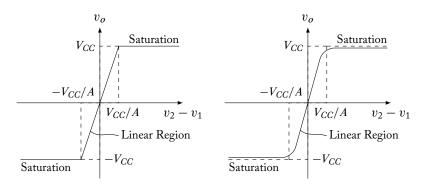

proportionality constant A is the called the *open loop gain*, whose significance will be detailed later. The second voltage constraint states that the output voltage is limited to the power supply rails. That is,  $v_o$  must lie between  $\pm V_{CC}$ . If the output reaches the limiting values, the amplifier is said to be saturated. In reality, the amplifier saturates at voltages slightly shy of  $\pm V_{CC}$  due to device characteristics within the OpAmp. So long as  $|v_o| < V_{CC}$ , the amplifier is operating in the linear region. Between the limiting values lies the "linear region" where the output voltage is related to the input voltage by the proportionality constant A. Figure 1.5a shows an idealized voltage transfer characteristic of an OpAmp. A more realistic voltage transfer characteristic is shown in Figure 1.5b where the amplifier response gradually tapers toward saturation at higher input voltages due to the characteristics of the circuit design internal to the chip.

From the data sheet for the  $\mu$ A741C, the typical open loop gain (designated as Large Signal Voltage Gain), A, is 200k. It is reasonable to assume that all OpAmps have very large voltage gain and that a first-order approximation of the voltage gain is:

$$A \approx \infty.$$

(1.4)

**Figure 1.5:** Transfer characteristics of (a) an ideal OpAmp and (b) more realistic "soft-limiting" OpAmp transfer characteristic.

In the 741 OpAmp, the absolute maximum supply voltages ( $V_{CC}$  and  $-V_{CC}$ ) are  $\pm 18$ V. Therefore, the output cannot exceed  $\pm 18$ V. Knowing the maximum value of the output voltage  $v_o$  and the typical A, the maximum difference between  $v_2$  and  $v_1$  is found to be:

$$(v_2 - v_1)_{\text{max}} = \frac{18\text{V}}{200,000} = 0.09 \,\text{mV}.$$

<sup>&</sup>lt;sup>6</sup>The power supply voltages are commonly called rails: they limit the output voltages of a functional electronic block.

<sup>&</sup>lt;sup>7</sup>A *transfer characteristic* is a graphical representation of the output as a function of the input. In this instance, the voltage input-output relationship is shown. A *transfer function* is usually a mathematical description of the output as a function of the input.

In most OpAmp applications this voltage level can be considered negligible. Therefore, in the linear region of operation, the input voltages are assumed to be equal:

$$v_1 \approx v_2. \tag{1.5a}$$

The input terminals of an OpAmp exhibit high input resistance: the  $\mu$ A741 typically has an input resistance of 2 M $\Omega$ . The input resistance of an ideal OpAmp is approximated as infinite.

$$R_i \approx \infty.$$

(1.6)

Within the linear region of operation the maximum current flowing between the two input terminals is given by:

$$i_{\text{input(max)}} = \frac{(v_2 - v_1)_{\text{max}}}{2 \,\text{M}\Omega} = \frac{0.09 \,\text{mV}}{2 \,\text{M}\Omega} = 45 \,\text{pA}.$$

The input currents,  $i_1$  and  $i_2$ , are extremely small and are considered to be approximately zero:

$$i_1 = i_2 \approx 0. \tag{1.5b}$$

The two relationships given in Equations (1.5a) and (1.5b) together form what is referred to as a "virtual short" between the inverting and non-inverting input terminals of the OpAmp. A virtual short implies that two terminals act in a *voltage sense* as if they were *shorted*, but *no current flows between the terminals*.

Kirchhoff's current law (KCL) can be used to sum the currents of an OpAmp. Since the input currents are very small, the resulting relationship is,

$$i_o = -(I_{C+} + I_{C-}). (1.7)$$

Equation (1.7) indicates that although the input currents are negligible, the output current is substantial. That is,  $i_0 \neq 0$ .

For completeness, the typical output resistance of a 741 OpAmp is 75  $\Omega$ . All OpAmps have low output resistance: Ideal OpAmps are considered to have zero-value output resistance.

$$R_o \approx 0.$$

(1.8)

Equations (1.2) to (1.8) define the *ideal OpAmp model*. These defining properties are summarized in Table 1.1.

The SPICE macromodel<sup>8</sup> for the  $\mu$ A741C OpAmp yields a value of A of approximately 195 k. The input and output impedances are complex and vary with input signal frequency. The real part of the input impedance dominates with a value of approximately 996 k $\Omega$ . The output impedance is essentially 50  $\Omega$  at frequencies above 100 Hz. The component parameters specified in the SPICE macromodel of the  $\mu$ A741C OpAmp and the typical specifications found in

$<sup>^8</sup>$ A SPICE macromodel is a complex subcircuit model of a device intended to correctly model all terminal performance characteristics of a device. The SPICE macromodel for the  $\mu$ A741C OpAmp was provided by MicroSim Corp.

**Table 1.1:** OpAmp characteristic property values

| OpAm                                  |                        | mp Value          |

|---------------------------------------|------------------------|-------------------|

| Property                              | Typical                | Ideal             |

| Gain, A                               | > 200,000              | $\infty$          |

| Input Resistance, $R_i$               | $> 2 \mathrm{M}\Omega$ | $\infty$          |

| Output Resistance, $R_o$              | $<75\Omega$            | 0                 |

| Input Voltage Difference, $v_2 - v_1$ | $< 0.1\mathrm{mV}$     | 0 (virtual short) |

| Input Current, $i_1$ or $i_2$         | $< 50 \mathrm{pA}$     | 0 (virtual short) |

| Output Voltage Limits                 | $ v_o  < V_{CC}$       | $ v_o  < V_{CC}$  |

the data sheet both lie within the acceptable range of parameter values found in manufactured components. Therefore, using either specification will yield acceptable results when designing a circuit using the  $\mu$ A741C.

The voltage and current constraints given are the parameters used to describe an *ideal* OpAmp model. By attaching external components to an OpAmp, a functional circuit can be designed. The significance of this exercise is to demonstrate the power of modelling active elements (in this case, an OpAmp) in terms of its current and voltage characteristics at the input and output ports. Although an understanding of the internal operation of the active device is desirable, circuits can be designed using the device's input and output port parameters. The terminal characteristics of the active device in conjunction with the Kirchhoff's current and voltage laws are used to analyze the circuit.

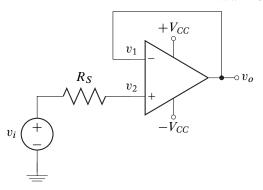

A simple application of an OpAmp is the unity gain buffer, which is primarily used to isolate electronic signals. A unity gain buffer or voltage follower is shown in Figure 1.6. The circuit can be analyzed using the voltage and current constraints given by Equations (1.5a) and (1.5b), respectively,

$$v_1 \approx v_2$$

and

$$i_1 = i_2 \approx 0.$$

The input signal voltage  $v_i$  is equal to  $v_2$  since negligible current flows into the positive input terminal of the OpAmp ( $i_2 = 0$ ): there is no voltage drop across  $R_s$ . Owing to the virtual short between the inverting and non-inverting terminals, the non-inverting terminal voltage is also at the same voltage level,  $v_i$ , that is,

$$v_i = v_2 = v_1.$$

Since the inverting terminal is directly connected to the output of the OpAmp,

$$v_o = v_1 = v_i$$

or

$$\frac{v_o}{v_1} = 1.$$

(1.9)

Figure 1.6: Unity gain buffer.

The voltage follower is called a unity gain *buffer* since it is an ideal impedance transformer. The input impedance of the voltage follower is very high and its output impedance is, for all practical purposes, zero. Verification of these impedance characteristics provides a useful exercise in the study of OpAmp properties.

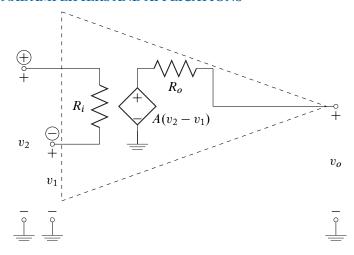

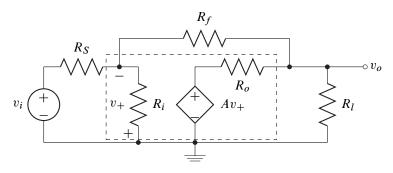

The input and output resistances of the voltage follower can be found by using the simplified equivalent circuit for the OpAmp. The simplified equivalent circuit, shown in Figure 1.7, differs from the ideal OpAmp model in that the equivalent circuit is a lumped parameter (resistors and sources) model of the OpAmp in the linear region of operation. It is a functional equivalent of the OpAmp which is not the actual circuitry in the OpAmp chip, but behaves functionally as an OpAmp to external circuitry (the principle is much the same as Thévenin or Norton equivalent circuits). The simplified OpAmp equivalent model shown here assumes frequency independent behavior: that is, the response of the amplifier is independent of signal frequency.

The current and voltage constraints in Equations (1.5a) and (1.5b) assumed in the ideal OpAmp model must be discarded when using the simplified equivalent model. Equation (1.2) is no longer valid due to the non-zero output resistance,  $R_o$ .

The voltage follower circuit is analyzed using the simplified equivalent circuit as shown in Figure 1.8. In the model,  $R_i = 2 \text{ M}\Omega$ ,  $R_o = 75 \Omega$ , and A = 200 k. Let  $R_S = 1 \text{ k}\Omega$ .

The current i is found by Kirchhoff's Voltage Law (KVL),

$$i = \frac{v_i - A(v_2 - v_1)}{R_i + R_O + R_S},\tag{1.10}$$

but *i* is also given by:

$$i = \frac{v_2 - v_1}{R_i}. (1.11)$$

<sup>&</sup>lt;sup>9</sup>In reality this frequency independence is not true. The frequency dependent nature of OpAmps will be discussed in 9 (Book 3).

Figure 1.7: Simplified equivalent circuit model of the OpAmp.

Figure 1.8: Voltage follower analysis with simplified equivalent OpAmp model.

Since the output terminal of a voltage follower is connected to the negative input terminal of the  $\mathrm{OpAmp}$ ,

$$v_o = v_1 \tag{1.12}$$

Equating Equations (1.10) and (1.11), substituting  $v_i$  for  $v_2$ , and solving for  $v_o/v_i$  yields the expression for voltage gain for the voltage follower:

$$\frac{v_o}{v_i} = 1 - \frac{R_i}{R_S + R_o + R_i (1 + A)}. (1.13)$$

Figure 1.9: Using a test source to find the Thévenin equivalent input resistance,  $R_{in}$ .

It can easily be seen that large values of the OpAmp gain, A, will lead to a voltage gain closely approximating unity. The parameter values for this example,  $R_i = 2 \,\mathrm{M}\Omega$ ,  $R_o = 75 \,\Omega$ ,  $R_S = 1 \,\mathrm{k}\Omega$ and  $A = 200 \,\mathrm{k}$ , result in:

$$\frac{v_o}{v_i} = 1 - 2.6875 \times 10^{-9} \approx 1. \tag{1.14}$$

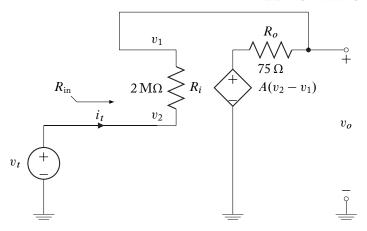

The input and output resistances of the voltage follower can be calculated using the simplified equivalent model. Thévenin equivalent resistances are found using the standard "test source" method. To calculate the input resistance, a test source,  $v_t$  is used to excite the circuit shown in Figure 1.9. Note that  $v_t$  is applied directly to  $v_2$ . The input resistance directly from the voltage source  $v_i$  in Figure 1.8 is found by adding  $R_S$  to the Thévenin resistance found at  $v_2$ . The Thévenin equivalent input resistance,  $R_{in}$ , is the ratio of the test voltage over the current delivered by the test source,

$$R_{in} = \frac{v_t}{i_t}. ag{1.15}$$

Using KVL, the current delivered by the test voltage,  $v_t$ , is

$$i_t = \frac{v_t - A(v_2 - v_1)}{R_i + R_o}. (1.16)$$

But

$$v_2 = v_t, \tag{1.17}$$

and, knowing the voltage drop across  $R_i$ ,

$$v_1 = v_t - i_t R_i. (1.18)$$

Substituting Equations (1.17) and (1.18) into (1.16) yields

$$i_t = \frac{v_t - Ai_t R_i}{R_i + R_o}. (1.19)$$

The Thévenin input resistance,  $R_{in}$ , is found by rearranging Equation (1.19),

$$R_{in} = \frac{v_t}{i_t} = R_i (1 + A) + R_o. {(1.20)}$$

For the given typical parameter values ( $R_i = 2 \,\mathrm{M}\Omega$ ,  $A = 200 \,\mathrm{K}$ , and  $R_o = 75 \,\Omega$ ), the input resistance can be calculated to be the very large value:  $R_{in} = 400 \times 10^9 \,\Omega$ . It is reasonable to assume that the input resistance of a unity gain buffer,  $R_{in}$  is, for all practical purposes, infinite.

#### Example 1.1

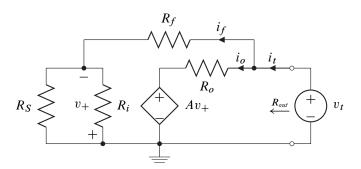

Determine the output resistance of an OpAmp voltage follower.

#### **Solution:**

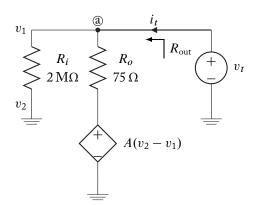

To find the output resistance,  $R_{out}$ , a test voltage source is connected to the output of the voltage follower to find the Thévenin equivalent resistance at the output. Note also that all independent sources must be zeroed. That is, all independent voltage sources are short circuited and all independent currents are open circuited. The circuit used to find  $R_{out}$  is shown in Figure 1.10.<sup>10</sup> To find the Thévenin equivalent output resistance, a test voltage source,  $v_t$  is connected at the

Figure 1.10: Simplified equivalent circuit for finding  $R_{out}$  of an OpAmp voltage follower.

output. The circuit draws  $i_t$  source current. The input at  $v_2$  has been short circuited to ground to set independent sources to zero.

<sup>&</sup>lt;sup>10</sup>In this example the resistance of the source connected to the input was considered to be zero: that is,  $R_s = 0$ . When the resistance of the source is not zero, it appears in series with the input resistance of the OpAmp,  $R_i$ . The effect of considering non-zero source resistance in the results of this example is insignificant.

Using the node voltage method of analysis by summing all currents flowing into node a yields:

$$i_t + \frac{v_2 - v_1}{R_i} + \frac{A(v_2 - v_1) - v_t}{R_o} = 0.$$

(1.21)

But

$$v_2 = 0$$

and  $v_1 = v_t$ . (1.22)

Then equation (1.21) is simplified to

$$i_t = \frac{R_o + (A+1) R_i}{R_o R_i} v_t, \tag{1.23}$$

and  $R_{out}$  is found to be:

$$R_{out} = \frac{v_t}{i_t} = \frac{R_o R_i}{R_o + (A+1) R_i}.$$

(1.24)

A typical value for the output resistance of the unity gain buffer,  $R_{out}$ , can be calculated using the given typical OpAmp values of  $R_i = 2 \,\mathrm{M}\Omega$ ,  $R_o = 75 \,\Omega$ , and  $A = 200 \,\mathrm{k}$ .  $R_{out}$ is found to be  $375 \mu\Omega$  which in most circuit applications can be considered essentially zero.

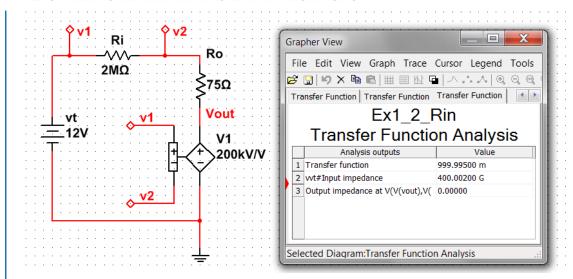

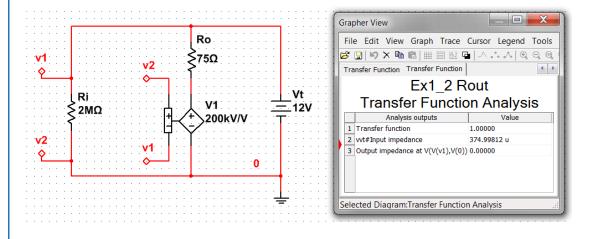

A SPICE simulation to determine the output resistance of a unity gain buffer using the circuit of Figure 1.10 is shown in Example 1.2. Solution #1 of Example 1.2 uses a SPICE-engine simulator (National Instruments MultiSim) solution using the Transfer Function Analysis command in conjunction with a source voltage to yield the gain and input and output resistances. Although the Transfer Function Analysis command is adequate for this particular example, a more general approach is to use a test source at the output as shown in Solution #2. This is particularly important when the input and output resistances are complex and are dependent on frequency. For instance, the input and output impedances of real OpAmps are complex and frequency dependent.

#### Example 1.2

Find the output resistance for a unity gain buffer using SPICE and the simplified OpAmp equivalent circuit.

#### Solution #1:

The National Instruments MultiSim solution using the Transfer Function Analysis command with a source voltage.

The Transfer Function Analysis command yields<sup>11</sup>  $R_{in} = 400 \text{ G}\Omega$  and  $R_{out} = 0 \Omega$ . The input resistance found here exactly matches the calculations using Equation (1.20). The output resistance is functionally the same value as found in Example 1.1.

<sup>11</sup>Many SPICE-based circuit simulators, as a default, insert a shunt resistance from analog nodes to ground [RSHUNT] to help eliminate problems such as "singular matrix" errors. Multisim<sup>TM</sup> uses a default value of  $10^{12}\Omega$  for RSHUNT: that value is not large enough to produce correct results for the circuit under consideration in this example. RSHUNT was removed from the list of default parameters in order to produce the results shown here.

#### Solution #2:

SPICE solution using a test source at the output terminal of the equivalent model. A test source at the output of the equivalent model yields  $R_{out}=375\,\mu\Omega$  which exactly matches the hand-calculated results of Example 1.1 and is, for all practical purposes, zero.

#### 1.3 BASIC APPLICATIONS OF THE OPAMP

Although the OpAmp can be used in infinite circuit configurations, several configurations have become basic electronic building blocks. These commonly-found OpAmp circuit configurations

are the inverting amplifier, summing amplifier, non-inverting amplifier, difference amplifier, integrator, and differentiator. All five configurations can be analyzed using the voltage and current constraints, and the ideal model of the OpAmp discussed in Sections 1.1 and 1.2.

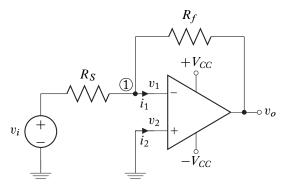

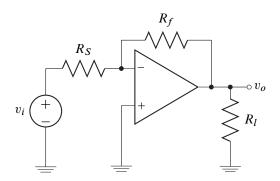

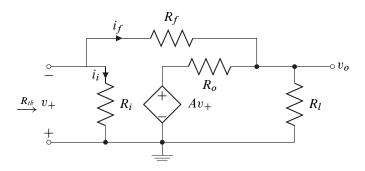

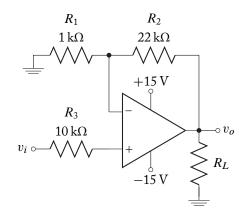

#### 1.3.1 INVERTING AMPLIFIER

The inverting amplifier configuration shown in Figure 1.11 amplifies and inverts the input signal in the linear region of operation. The circuit consists of a resistor  $R_S$  in series with the voltage source  $v_i$  connected to the inverting input of the OpAmp. The non-inverting input of the OpAmp is short circuited to ground (common). A resistor  $R_f$  is connected to the output and provides a negative feedback path to the inverting input terminal. Because the output resistance of the OpAmp is nearly zero, the output voltage  $v_o$  will not depend on the current that might be supplied to a load resistor connected between the output and ground.

For most OpAmps, it is appropriate to assume that their characteristics are approximated closely by the ideal OpAmp model of Section 1.2. Therefore, analysis of the inverting amplifier can proceed using the voltage and current constraints of Equations (1.5a) and (1.5b),

$$v_1 = v_2$$

,

and

$$i_1 = i_2 \approx 0.$$

Figure 1.11: The inverting amplifier configuration.

Since  $v_2$  is connected to the common or ground terminal,

$$v_2 = 0.$$

<sup>&</sup>lt;sup>12</sup>Further detailed discussion of feedback theory and the implication of negative feedback is found in 8 (Book 2). Analysis of the OpAmp circuits in this chapter will rely on standard circuit analysis techniques.

Node 1 is said to be a virtual ground due to the virtual short circuit between the inverting and non-inverting terminals (which is grounded) as defined by the voltage constraint,

$$v_1 = v_2 = 0. (1.25)$$

The node voltage method of analysis is applied at node 1,

$$0 = \frac{v_i - v_1}{R_S} + \frac{v_0 - v_1}{R_f} + i_1. \tag{1.26}$$

By applying Equation (1.25), obtained from the virtual short circuit, and the constraint on the current  $i_1$  as defined in Equation (1.5b), Equation (1.26) is simplified to

$$0 = \frac{v_i}{R_S} + \frac{v_o}{R_f}. (1.27)$$

Solving for the voltage gain,  $v_o/v_i$ ,

$$\frac{v_o}{v_i} = -\frac{R_f}{R_S} \tag{1.28}$$

Notice that the voltage gain is dependent only on the ratio of the resistors external to the OpAmp,  $R_f$  and  $R_S$ . The amplifier increases the amplitude of the input signal by this ratio. The negative sign in the voltage gain indicates an inversion in the signal.

The output voltage is also constrained by the supply voltages  $V_{CC}$  and  $-V_{CC}$ ,

$$|v_o| < V_{CC}$$

Using Equation (1.28), the maximum resistor ratio  $R_f/R_s$  for a given input voltage  $v_i$  is

$$\frac{R_f}{R_S} < \left| \frac{V_{CC}}{v_i} \right|. \tag{1.29}$$

The input resistance of the inverting amplifier can be readily determined by applying the voltage constraint:  $v_1 = v_2 = 0$ . Therefore, the resistance that the signal source  $v_i$  encounters is simply  $R_S$  due to the virtual short to ground at the inverting terminal. Then  $R_S$  must be large for a high input resistance. If  $R_S$  is large,  $R_f$  must be very large to achieve large gain,  $R_f/R_s$ . In some instances,  $R_f$  may be prohibitively high. Therefore, in most applications, the input resistance of the inverting amplifier is low to moderate.

<sup>&</sup>lt;sup>13</sup>The non-ideal characteristics of OpAmps place constraints on externally connected elements. A discussion of these constraints is found in Section 1.5 of this chapter.

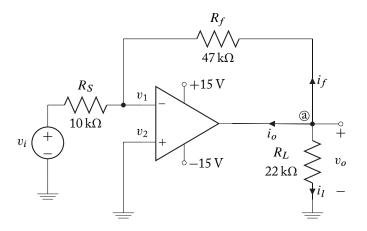

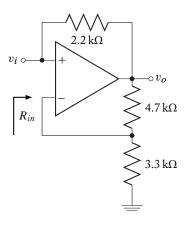

#### Example 1.3

For the circuit shown in Figure 1.12, find the gain and  $i_o$ . If  $v_i = 2 \sin \omega_o t$  V, what is the output? What input voltage amplitude will cause the amplifier to saturate?

**Figure 1.12:** Inverting amplifier with load resistor,  $R_{\rm L}$ .

#### **Solution:**

The output voltage  $v_o$  is independent of the load resistor,  $R_L$ , because of the low output resistance of the OpAmp. Therefore, the gain of the amplifier is

$$\frac{v_o}{v_i} = -\frac{R_f}{R_S}$$

$$= -\frac{47 \,\mathrm{k}\Omega}{10 \,\mathrm{k}\Omega} = -4.7.$$

Using KCL at node a,

$$0 = i_o + i_f + i_l.$$

The currents  $i_f$  and  $i_l$  are

$$i_1 = -\frac{v_o}{22000} = -\frac{4.7 \times 2 \sin{(\omega_o t)}}{22000}$$

and

$$i_f = -\frac{v_o}{47000} = -\frac{4.7 \times 2 \sin(\omega_o t)}{47000}.$$

Solving for  $i_o$  yields,

$$i_O = \left(\frac{1}{47000} + \frac{1}{22000}\right) \times 4 \times 4.7 \sin(\omega_o t)$$

= 1.255 \sin \omega\_o t \mA.

For an input voltage signal of  $v_i = 2 \sin \omega_o t V$ ,

$$v_o = \frac{v_o}{v_i} \times 2 \sin(\omega_o t) = -4.7 \times 2 \sin(\omega_o t) = -9.4 \sin(\omega_o t) \text{ V}.$$

For operation in the linear region of the amplifier, the input amplitude must not exceed,

$$|v_i| < \frac{+V_{CC}}{R_f/R_S} < \frac{15}{4.7} = 3.19 \text{ V}.$$

Input signal amplitudes greater than or equal to 3.19 will cause the amplifier to saturate.

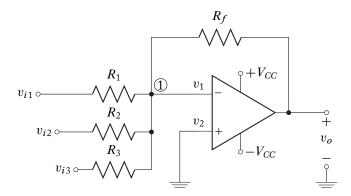

#### 1.3.2 SUMMING AMPLIFIER

The output voltage of a summing amplifier is an inverted, amplified sum of the input voltages. A summing amplifier can theoretically have a large number of input voltages. Figure 1.13 shows a summing amplifier with three inputs,  $v_{i1}$ ,  $v_{i2}$ , and  $v_{i3}$ .

Using the node voltage method by summing the current entering node 1 gives

$$0 = \frac{v_{i1} - v_1}{R_1} + \frac{v_{i2} - v_1}{R_2} + \frac{v_{i3} - v_1}{R_3} + \frac{v_o - v_1}{R_f}$$

(1.30)

The virtual short between input terminals of the OpAmp leads to:

$$v_1 = v_2 = 0.$$

Therefore, Equation (1.30) simplifies to,

Figure 1.13: Summing amplifier with three input signals.

$$0 = \frac{v_{i1}}{R_1} + \frac{v_{i2}}{R_2} + \frac{v_{i3}}{R_3} + \frac{v_o}{R_f}.$$

(1.31)

19

Solving for the output voltage  $v_o$  yields,

$$v_o = -\left(\frac{R_f}{R_1}v_{i1} + \frac{R_f}{R_2}v_{i2} + \frac{R_f}{R_3}v_{i3}\right). \tag{1.32}$$

The output voltage is an inverted sum of scaled input voltages.

A particularly useful case occurs when  $R_1 = R_2 = R_3 = R_S$ . In this case, Equation (1.32) is simplified to,

$$v_o = -\frac{R_f}{R_s} \left( v_{i1} + v_{i2} + v_{i3} \right). \tag{1.33}$$

The number of input signal voltages may be increased to meet the requirements of the application. For n input signals,

$$v_o = -\frac{R_f}{R_s} \sum_{j=1}^n v_{ij}. {(1.34)}$$

## Example 1.4

Two voltage signals,

$$v_{i1} = 2 \cos(\omega_o t + 25^\circ) \text{ V}$$

and  $v_{i2} = 1.5 \cos(\omega_o t - 35^\circ) \text{ V}$

are added by the summing amplifier in Figure 1.14.

Find the output voltage,  $v_o$ .

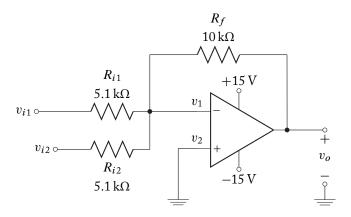

Figure 1.14: Summing amplifier with two input voltages.

## **Solution:**

Since  $R_1 = R_2$ , the expression for the output voltage is,

$$v_o = -\frac{R_f}{R_s} \left( v_{i1} + v_{i2} \right).$$

The input voltages in this example are sinusoids of the same frequency. Therefore, the two input voltages can be combined using phasor representation,

$$V_i = V_{i1} + V_{i2}$$

.

The sum of the voltages is,

$$v_i = v_{i1} + v_{i2}$$

=  $2\cos(\omega_o t + 25^\circ) + 1.5\cos(\omega_o t - 35^\circ)$ .

The sum of the voltages in phasor representation is,

$$V_{i} = V_{i1} + V_{i2}$$

$$= 2 \angle 25^{\circ} + 1.5 \angle -35^{\circ}$$

$$= (1.81 + j0.845) + (1.23 - j0.860)$$

$$= 3.04 - j0.015$$

$$= 3.04 \angle -0.285^{\circ} \text{ V}.$$

The output voltage in phasor notation is,

$$\mathbf{V_0} = -\frac{R_f}{R_1} \mathbf{V_i}$$

=  $-\left(\frac{10k}{5.1k}\right) (3.04 \angle -0.285^\circ)$

=  $-5.96 \angle -0.285^\circ \text{ V}.$

In time domain notation, the output voltage is,

$$v_o = -5.96 \cos(\omega_o t - 0.285^\circ) \text{ V}.$$

Note that the resulting output voltage requires the use of the phase of the two input signals. The output voltage in this case is the amplifier gain,  $-R_f/R_1 = -1.96$  multiplied by the phasor sum of the two input voltages. This example demonstrates that proper attention to the phase and frequency of the input signals is required when designing and analyzing circuits.

#### 1.3.3 NON-INVERTING AMPLIFIER

A non-inverting amplifier is shown in Figure 1.15 where the source is represented by  $v_S$  and a series resistance  $R_S$ .

The analysis of the non-inverting amplifier in Figure 1.15 assumes an ideal OpAmp operating within its linear region. The voltage and current constraints at the input to the OpAmp yield the voltage at node 1,

$$v_1 = v_2 = v_S,$$

Figure 1.15: Non-inverting amplifier configuration.

since  $i_1 = i_2 = 0$ . Using the node voltage method of analysis, the sum of the currents flowing into node 1 is,

$$0 = \frac{0 - v_1}{R_G} + \frac{v_o - v_1}{R_f}. ag{1.35}$$

Solving for the output voltage  $v_o$  using the voltage constraints,  $v_1 = v_S$

$$v_o = v_i \left( 1 + \frac{R_f}{R_G} \right). \tag{1.36}$$

The gain of the non-inverting amplifier is,

$$\frac{v_o}{v_i} = 1 + \frac{R_f}{R_G}. (1.37)$$

Unlike the inverting amplifier, the non-inverting amplifier gain is positive. Therefore, the output and input signals are ideally in phase. The amplifier will operate in its linear region when,

$$1 + \frac{R_f}{R_G} < \left| \frac{V_{CC}}{v_s} \right|. \tag{1.38}$$

Note that, like the inverting amplifier, the gain is a function of the external resistors  $R_f$  and  $R_G$ .

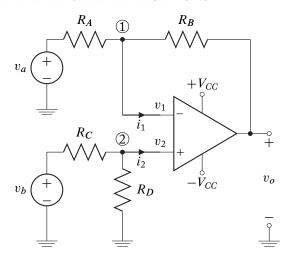

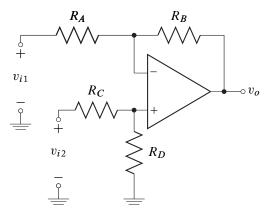

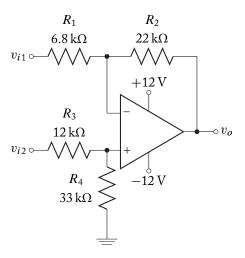

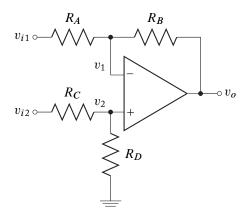

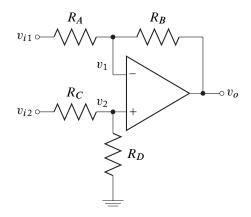

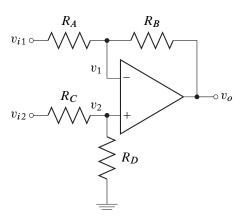

### 1.3.4 DIFFERENCE AMPLIFIER

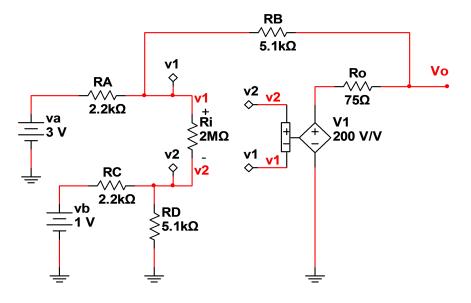

The output voltage signal of a difference amplifier is proportional to the difference of the two input voltage signals. A schematic of a difference amplifier is shown in Figure 1.16.

**Figure 1.16:** Difference amplifier with input voltages  $v_a$  and  $v_b$ .

By assuming an ideal OpAmp operating in the linear region, the current constraints can be used to yield the voltages at nodes 1 and 2 as a simple voltage division at the non-inverting input:

$$v_1 = v_2 = v_b \left( \frac{R_D}{R_C + R_D} \right). {(1.39)}$$

The node voltage method of analysis is used to determine the output voltage  $v_o$  with respect to the input voltages  $v_a$  and  $v_b$ ,

$$0 = \frac{v_a - v_1}{R_A} + \frac{v_o - v_1}{R_B}. (1.40)$$

Solving for the output voltage  $v_o$  yields,

$$v_o = \frac{R_B}{R_A} (v_1 - v_a) + v_1. (1.41)$$

Substituting Equation (1.39) into (1.41) provides the output voltage as a function of the input voltages,

$$v_o = \frac{R_D}{R_C + R_D} \left( \frac{R_B}{R_A} + 1 \right) v_b - \frac{R_B}{R_A} v_a. \tag{1.42}$$

The expression for the output voltage in Equation (1.42) can be simplified for the particular case where the resistor ratios are given by:

$$\frac{R_A}{R_B} = \frac{R_C}{R_D}. (1.43)$$

By applying the ratio of Equation (1.43), the output voltage in Equation (1.42) is reduced to a scaled difference of the input voltages,

$$v_o = \frac{R_B}{R_A} (v_b - v_a). {(1.44)}$$

The difference amplifier is commonly used in circuits that require comparison of two signals to control a third (or output) signal. For instance,  $v_a$  could be a voltage reading representing temperature from a thermistor (a resistor that changes values with temperature) circuit and  $v_b$  a reference voltage representing a temperature setting. The output of the difference amplifier would then be the deviation of the measured temperature from the reference temperature setting.

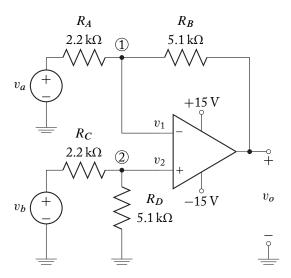

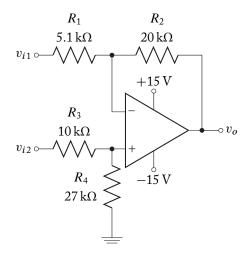

#### Example 1.5

The difference amplifier in Figure 1.17 has an input voltage  $v_a = 3 \text{ V}$ . What values of  $v_b$  will result in operation in the linear region?

Figure 1.17: Difference amplifier of Example 1.5.

#### **Solution:**

The limits on the output voltage are determined by the power supply rail voltages. In this example, the supply voltages are  $+15\,\mathrm{V}$  and  $-15\,\mathrm{V}$ . Therefore, the output voltage must be,

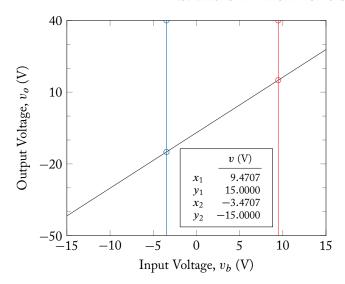

$$-15 \text{ V} < v_o < +15 \text{ V}.$$

Since  $\frac{R_A}{R_B} = \frac{R_C}{R_D}$  the input voltage  $v_b$  from Equation (1.44) can be calculated,

$$v_b = \frac{R_A}{R_B} v_o + v_a.$$

Substituting  $R_A = 2.2 \,\mathrm{k}\Omega$  and  $R_B = 5.1 \,\mathrm{k}\Omega$  into the equation for  $v_b$  yields for the upper and lower limits of the output voltage,

$$v_o = +15 \,\text{V}$$

:  $v_b = 9.47 \,\text{V}$ ,

and

$$v_o = -15 \,\text{V}$$

:  $v_b = -3.47 \,\text{V}$ .

Then the input voltage range for  $v_b$  to insure linear operation of the amplifier is,

$$-3.47 \,\mathrm{V} < v_o < 9.47 \,\mathrm{V}$$

.

The Multisim schematic and simulation results are given below. The simplified model of the OpAmp is used. The voltage  $v_b$  is swept from  $-15\,\mathrm{V}$  to  $15\,\mathrm{V}$ . The output voltage is at node  $V_o$ . Note that the node voltage at the output extends well above  $15\,\mathrm{V}$  and below  $-15\,\mathrm{V}$ . The excursion occurs because the simplified OpAmp model assumes operation in the linear region. Therefore, care must be taken when using this model to take into account the limits on the output voltage. As shown in the output plot, the range of values for  $v_b$  is from  $-3.47\,\mathrm{V}$  to  $9.47\,\mathrm{V}$  as indicated by the cursors for output voltages of  $-15\,\mathrm{V}$  and  $15\,\mathrm{V}$ , respectively.

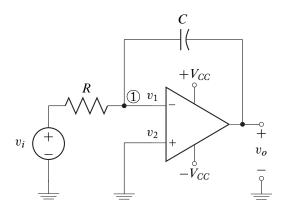

#### 1.3.5 **INTEGRATOR**

The integrator is commonly used in signal generation or processing applications. The name of the circuit is accurately descriptive: the integrator performs an integration operation on the input signal. An integrator is shown in Figure 1.18. The circuit is similar to the inverting amplifier with the feedback resistor  $R_f$  replaced by a capacitor C.

Figure 1.18: Integrator circuit.

With an ideal OpAmp operating in its linear region, the node voltage method of analysis can be applied at node 1 using the OpAmp voltage and current constraints,

$$0 = \frac{v_i - v_1}{R} + C \frac{d}{dt} (v_o - v_1). \tag{1.45}$$

But  $v_1 = 0$  due to the virtual ground so,

$$0 = \frac{v_i}{R} + C \frac{dv_o}{dt}. ag{1.46}$$

Solving for  $v_o$  yields,

$$v_o = -\frac{1}{RC} \int v_i \ dt. \tag{1.47}$$

Equation (1.47) shows that the output voltage of an integrator circuit is a product of the reciprocal of the RC time constant and the integral of the inverted input signal.

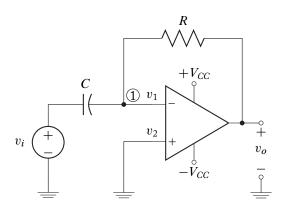

#### 1.3.6 DIFFERENTIATOR

If the capacitor and resistor positions in the integrator schematic are switched, the circuit performs a differentiation operation on the input signal. The resulting circuit is shown in Figure 1.19.

Figure 1.19: Differentiator circuit.

The analysis of the differentiator circuit is similar to the integrator. Apply the node voltage method of analysis at node 1 assuming ideal OpAmp characteristics to yield,

$$0 = C\frac{d(v_i - v_1)}{dt} + \frac{v_o - v_1}{R}$$

(1.48)

Using the voltage constraint  $v_1 = v_2 = 0$ , Equation (1.48) simplifies to,

$$0 = C\frac{dv_i}{dt} + \frac{v_o}{R} \tag{1.49}$$

The output voltage  $v_o$  is therefore,

$$v_o = -RC\frac{dv_i}{dt}. (1.50)$$

Equation (1.50) shows that the output voltage of a differentiator circuit is a product of the RC time constant and the derivative of the inverted input signal.

#### **DIFFERENTIAL AMPLIFIERS** 1.4

A differential amplifier is any two-input amplifier that has an output proportional to the difference of the inputs. The defining equation for a differential amplifier is then:

$$y_o = A(x_{i1} - x_{i2}), (1.51)$$

where the output,  $y_o$ , and the inputs  $\{x_i\}$  could be either voltages or currents. Previous discussions in this chapter have explored two differential amplifiers: the difference amplifier (shown in Figure 1.20) and the basic OpAmp itself. Each of these two examples has an output voltage that is proportional to the difference of two input voltages. In the case of the difference amplifier, the output expression was derived to be:

$$v_o = \frac{R_B}{R_A} \left( v_{i2} - v_{i1} \right), \tag{1.52}$$

if the resistor values were chosen so that

$$\frac{R_A}{R_B} = \frac{R_C}{R_D}. ag{1.53}$$

Ideally this amplifier (or any differential amplifier) is sensitive only to the difference in the two

Figure 1.20: A Difference Amplifier.<sup>14</sup>

input signals, and is completely insensitive to any common component of the two signals. That is, if the difference in inputs remains constant, the output should not vary if the average value of the two inputs changes. Unfortunately, a differential amplifier rarely meets this goal, and the output has a slight dependence on the average of the input signals. The output for this type of imperfect differential amplifier is given by:

$$v_o = A_{DM}v_{iDM} + A_{CM}v_{iCM} = A_{DM}(v_{i2} - v_{i1}) + A_{CM}\left(\frac{v_{i2} + v_{i1}}{2}\right), \tag{1.54}$$

where

$A_{DM}$  = the amplification of the input signal difference,  $v_2 - v_1$ ,

and

$$A_{CM}$$

= the amplification of the input signal average,  $\frac{(v_2+v_1)}{2}$ .

The *quality* of a differential amplifier is displayed in its ability to amplify the differential signal while suppressing the common signal. A measure of this quality is the ratio of the differential gain to the amplification of the average (or common) part of the input signals. The measure of quality is named *Common-mode rejection ratio* (CMRR) and is usually expressed in decibels (dB). The defining equation for CMRR is:

$$CMRR = 20 \log_{10} \left| \frac{A_{DM}}{A_{CM}} \right|. \tag{1.55}$$

Unfortunately, usual analysis procedures do not produce an expression in the form of Equation (1.54): the differential-mode gain,  $A_{DM}$ , and the common-mode gain,  $A_{CM}$ , are not the usual results of analysis. A more typical result of analysis procedures is:

$$v_o = A_1 v_{i1} + A_2 v_{i2}. (1.56)$$

A conversion between the two output expressions can be obtained by realizing that:

$$v_{i1} = \frac{(v_{i2} + v_{i1})}{2} - \frac{(v_{i2} - v_{i1})}{2} = v_{iCM} - \frac{1}{2}v_{iDM}, \tag{1.57a}$$

and

$$v_{i2} = \frac{(v_{i2} + v_{i1})}{2} + \frac{(v_{i2} - v_{i1})}{2} = v_{iCM} + \frac{1}{2}v_{iDM}.$$

(1.57b)

If Equations (1.57a) and (1.57b) are combined with Equation (1.56) the result is:

$$v_o = \left(\frac{A_2 - A_1}{2}\right)(v_{i2} - v_{i1}) + (A_1 + A_2)\left(\frac{(v_{i2} + v_{i1})}{2}\right),\tag{1.58}$$

The conclusions easily drawn from Equations (1.58) and (1.54) are:

$$A_{DM} = \left(\frac{A_2 - A_1}{2}\right)$$

and  $A_{CM} = (A_1 + A_2)$ . (1.59)

A good differential amplifier has  $A_1 \approx -A_2$ : the differential-mode gain will be large and the common-mode gain small. The CMRR will be large for a good differential amplifier: as an example, the  $\mu$ A741 OpAmp has a typical CMRR of 90 dB with a guaranteed minimum CMRR of 70 dB. <sup>15</sup>

#### Example 1.6

The difference amplifier of Figure 1.20 is constructed with an ideal OpAmp and 1% tolerance resistors of nominal values 2.2 k $\Omega$  and 5.1 k $\Omega$ . The resistors were measured and found to have the following resistance values:

$$R_A = 2.195 \,\mathrm{k}\Omega$$

$R_C = 2.215 \,\mathrm{k}\Omega$

$R_B = 5.145 \,\mathrm{k}\Omega$   $R_D = 5.085 \,\mathrm{k}\Omega$ .

Determine gain of the differential amplifier and its common-mode rejection ratio.

#### **Solution:**

The design gain of this amplifier is:

$$A = \frac{R_B}{R_A} = \frac{5.1 \,\mathrm{k}\Omega}{2.2 \,\mathrm{k}\Omega} = 2.318.$$

However, this value is based on the assumption of equal resistor ratios:

$$\frac{R_A}{R_B} = \frac{R_C}{R_D}.$$

The quality of this difference amplifier depends strongly on whether the resistor ratio described in Equation (1.53) is *exactly* valid. In this case,  $0.42663 \neq 0.43559$ . Typical resistor variation leads to the conclusion that the Equation (1.53) is slightly in error and the more exact expression for the output voltage as a function of the inputs is more correct:

$$v_o = \frac{R_D}{R_C + R_D} \left( \frac{R_B}{R_A} + 1 \right) v_{i2} - \frac{R_B}{R_A} v_{i1}.$$

This input-output transfer function is of the general form of Equation (1.56):

$$v_o = A_1 v_{i1} + A_2 v_{i2}.$$

<sup>&</sup>lt;sup>15</sup>CMRR is dependent on external circuitry as well as the fundamental properties of an OpAmp. The condition under which the  $\mu$ A741 measurements is made is: the output resistance of the source (and any series resistance between the source and the OpAmp) must be less than 10 kΩ.

where

$$A_2 = \frac{R_D}{R_C + R_D} \left( \frac{R_B}{R_A} + 1 \right) \quad \text{and} \quad A_1 = -\frac{R_B}{R_A}.$$

The common-mode and differential-mode gains can now be evaluated using the correct gain expression and Equations (1.59).

$$A_2 = \frac{5.085}{2.215 + 5.085} \left( \frac{5.145}{2.195} + 1 \right) = 2.329$$

and  $A_1 = -\frac{5.145}{2.195} = -2.344$

therefore

$$A_{DM} = 2.337$$

and  $A_{CM} = -0.01464$

The CMRR is then obtained using Equation (1.55):

CMRR =

$$20 \log_{10} \left| \frac{A_{DM}}{A_{CM}} \right| = 20 \log |-159.6| = 44.06 \,\mathrm{dB}.$$

The ratio of differential-mode gain to common-mode gain is about 160: this is only a moderately good differential amplifier. A good circuit designer would notice that the resistors in this example were paired in the worst possible manner. If the physical resistors used for  $R_A$  and  $R_C$  were exchanged, the resistor ratios in each gain path would be more nearly exact:  $0.4305 \gg 0.4317$ . Continuing with the gain calculations for this new configuration leads to:

$$A_2 = \frac{5.085}{2.195 + 5.085} \left( \frac{5.145}{2.215} + 1 \right) = 2.321$$

and  $A_1 = -\frac{5.145}{2.215} = -2.323$

with

$$A_{DM} = 2.322$$

and  $A_{CM} = -0.00186$

which results in a CMRR of:

CMRR =

$$20 \log_{10} \left| \frac{A_{DM}}{A_{CM}} \right| = 20 \log |-1248.0| = 61.92 \,\mathrm{dB}$$

Rearranging the resistors has brought an improvement in the CMRR of almost 18 dB: the ratio of gains has been improved by a factor of about 7.8. Obviously care must be taken in the choice and placement of element values to provide the optimum amplifier.

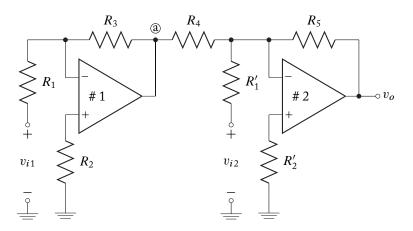

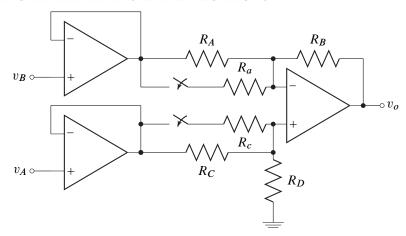

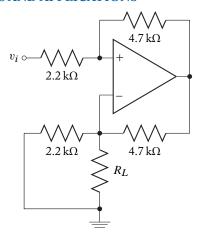

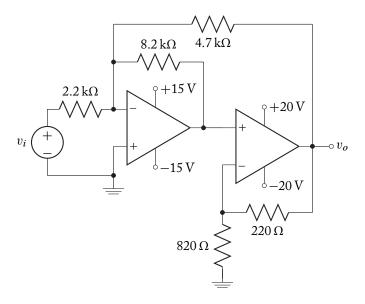

Differential amplifiers are not restricted to circuits with single OpAmps. It is possible to construct a differential amplifier without any OpAmps, while many differential amplifiers have three or more OpAmps as essential elements. Figure 1.21 shows the basic schematic representation of an instrumentation amplifier using two OpAmps. Instrumentation amplifiers are high performance voltage amplifiers that are primarily used for the initial amplification of signals from a variety of types of transducers. They are available packaged as a single item in a DIP package

or can be realized with discreet components. Packaged instrumentation amplifiers usually have greater control on the factors contributing to CMRR and are often the advantageous choice for the circuit designer.

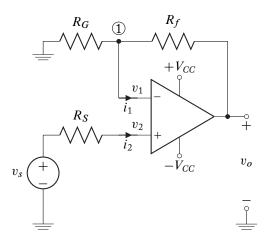

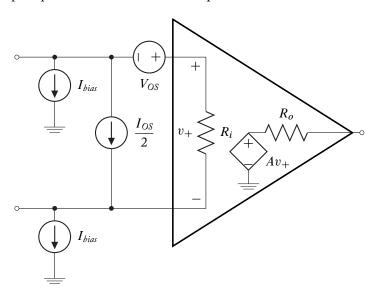

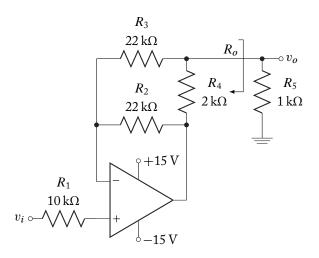

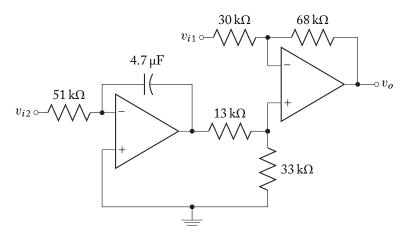

The basic topology of this particular instrumentation amplifier is that of an inverting amplifier connected in series with a summing amplifier. The extra resistors at the positive terminals of each OpAmp,  $R_2$  and  $R'_2$ , serve no obvious function if the OpAmps are considered to be ideal: their function is to reduce the effects of input parameter variations which are non-ideal properties of OpAmps. 16 The inversion of  $v_{i1}$  prior to summation allows for the output of the amplifier to be a multiple of the difference of the two inputs. This particular circuit topology also allows, with appropriate external resistor choices, for large (on the order of 100 V) input voltages.

Figure 1.21: An instrumentation amplifier with high input voltage capability.

Analysis of this amplifier begins, as usual, with the assumption that each OpAmp is nearideal: the input are virtually-shorted, the gain is infinite, the input resistance is infinite, and the output resistance is zero. Since no current flows into the inputs of either OpAmp, there is no voltage drop across the resistors,  $R_2$  and  $R'_2$ . The OpAmp positive input terminals are therefore at ground potential: each OpAmp circuit acts in the same manner as if its positive terminal were directly connected to ground. The zero output resistance of the first OpAmp implies that the remainder of the circuit does not affect its output, and the voltage at node a is obtained from the gain equation for an inverting amplifier:

$$v_a = -\frac{R_3}{R_1} v_{i1}. (1.60)$$

The zero output resistance of the first OpAmp circuit also implies that it acts as a perfect voltage source input to the summing amplifier of the second OpAmp. The output of the summing

<sup>&</sup>lt;sup>16</sup>The effects of input parameter variations on OpAmp performance is discussed in Section 1.5.

amplifier is then given by:

$$v_o = -\frac{R_5}{R_4} v_a - \frac{R_5}{R_1'} v_{i2}; (1.61)$$

or, with the results of Equation (1.60),

$$v_o = \frac{R_5 R_3}{R_4 R_1} v_{i1} - \frac{R_5}{R_1'} v_{i2}. \tag{1.62}$$

If proper resistor value choices are made, this instrumentation amplifier becomes a true differential amplifier. The necessary restriction on the resistor values to create a differential amplifier is:

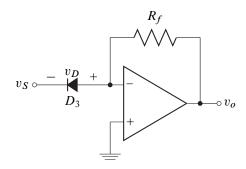

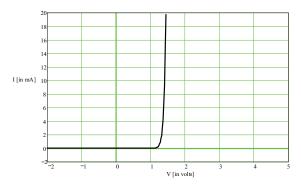

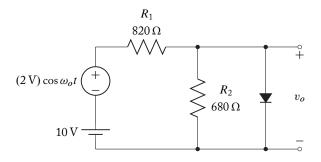

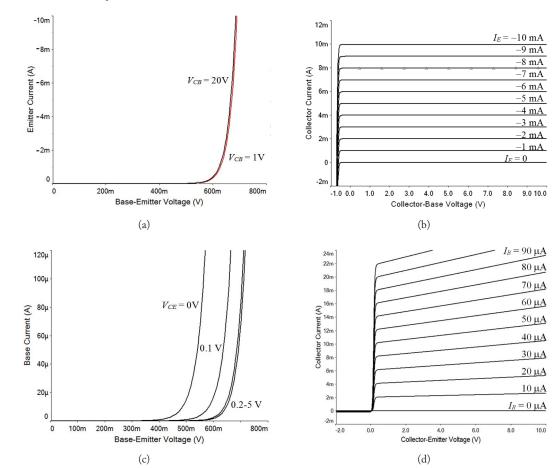

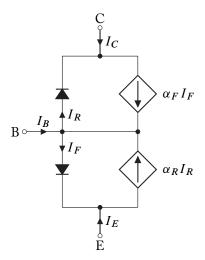

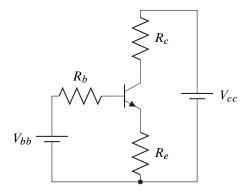

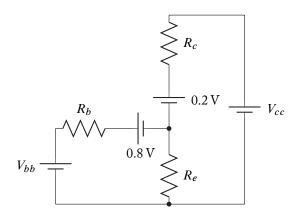

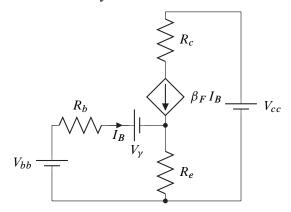

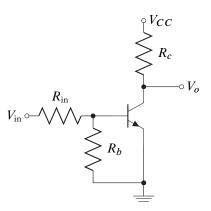

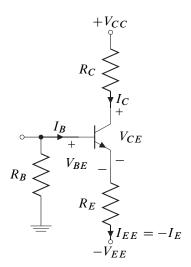

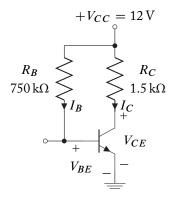

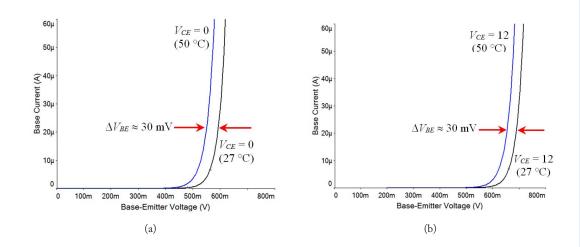

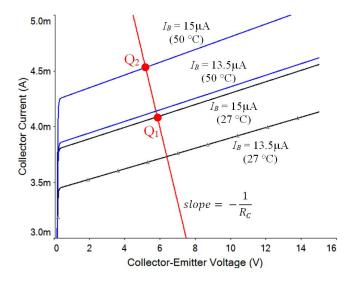

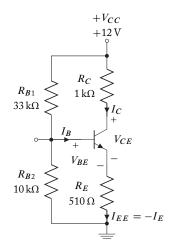

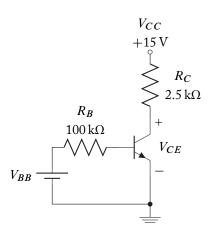

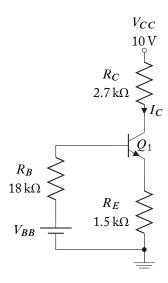

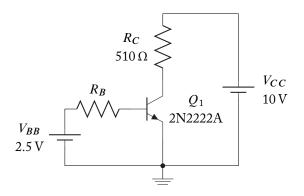

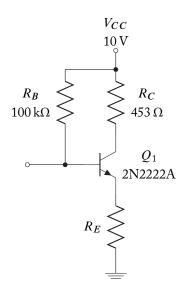

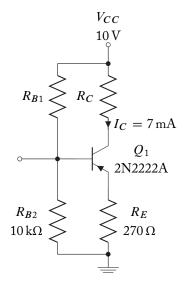

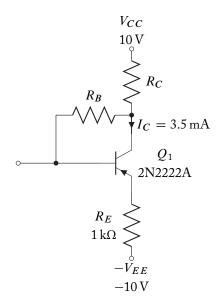

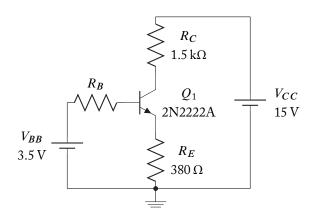

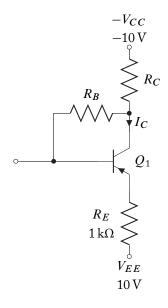

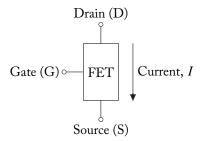

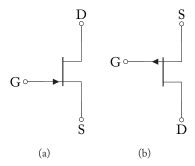

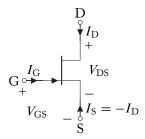

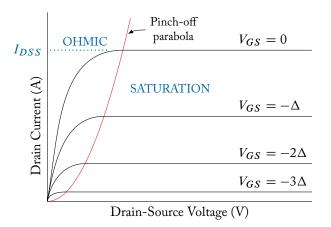

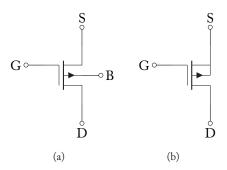

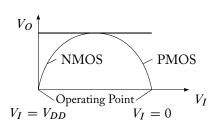

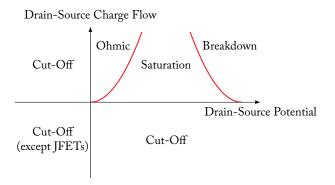

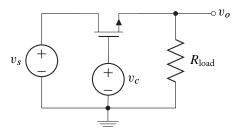

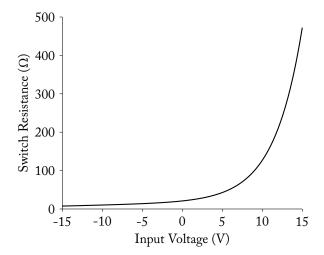

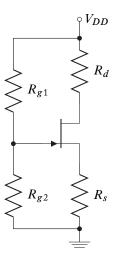

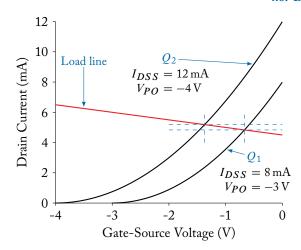

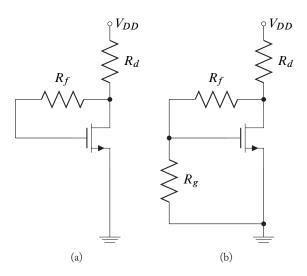

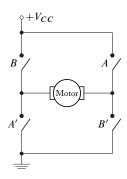

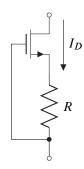

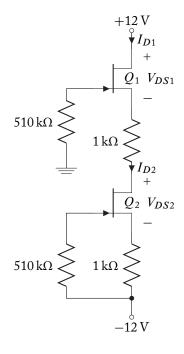

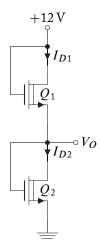

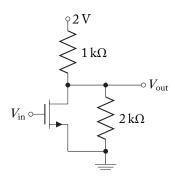

$$\frac{R_1 R_4}{R_3} = R_1'. (1.63)$$